중국 복단대학 연구팀이 반도체로 실리콘 대신 이황화몰리브덴(MoS2)을 사용한 32비트 RISC-V 프로세서를 개발했다고 학술지 네이처에 게재된 논문에서 발표했다.

반도체 업계에는 오랫동안 반도체 집적밀도는 18~24개월마다 2배로 증가하고 칩 성능이 2배가 되어도 더 소형화가 진행된다는 무어의 법칙이 경험칙으로 존재하며 제조사 목표로 기능해 왔다. 하지만 최근에는 무어의 법칙이 한계에 가까워지고 있다는 지적이 있다.

이런 상황에서 주목받고 있는 게 실리콘을 대체할 새로운 반도체 재료인 2차원 물질이다. 3차원 결정인 실리콘은 가로와 세로 뿐 아니라 깊이 방향으로도 구조를 갖고 있기 때문에 미세화 기술을 향상시켜도 결국 한계에 도달해 더 이상 작게 만들 수 없는 단계에 이른다고 한다. 이에 비해 단일 평면에서 반복되는 화학 결합을 가진 2차원 물질은 기껏해야 원자 1개~수 개 정도의 두께만 가지므로 실리콘이 가진 제한을 회피할 수 있을 것으로 기대되고 있다.

이번 연구팀이 프로세서 제조에 사용한 건 2차원 재료 중 하나인 이황화몰리브덴. 이황화몰리브덴 화학 결합은 황과 몰리브덴이 지그재그로 배열된 화학 결합을 갖고 있으며 구성 원자보다는 조금 두껍지만 상당히 얇은 재료가 된다.

많은 연구자 노력으로 이미 2차원 물질에서 불과 몇 원자 분량 두께 트랜지스터를 제조하는 데는 성공했다. 하지만 원자 수준 정밀도로 완전한 집적회로를 구축하는 건 어려워 지금까지는 최대 수백 개 트랜지스터를 집적하는 데 그쳤다.

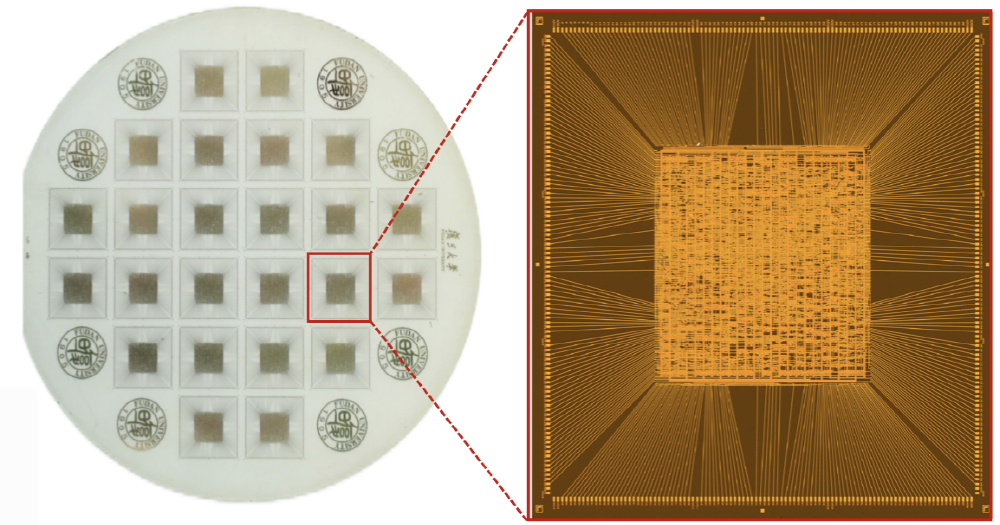

복단대학 연구팀은 5년간 연구개발 끝에 사파이어 기판 위에 웨이퍼 크기 이황화몰리브덴 시트를 생성하고 이황화몰리브덴 트랜지스터 5,900개를 집적한 RISC-V 프로세서를 개발하는 데 성공했다.

연구팀이 구축한 데모 디바이스는 일부에 도전 재료로 그래핀을 사용했다. 또 배선에 알루미늄과 금이라는 2가지 다른 금속을 사용하고 배선 재료와 내장된 재료를 통해 각 트랜지스터 임계전압을 조정했다. 이 배선과 재료 조합은 기계학습을 사용해 특정됐다.

기능적인 회로를 만들기 위해 연구팀은 논리 게이트 25개를 모두 만들고 그 중 기능한 논리 게이트 18개로 프로세서를 구축했다. 최종적으로 프로세서 제조 전체 수율은 99.9% 이상에 달했다고 보고됐다.

이렇게 제조된 이황화몰리브덴 프로세서에는 트랜지스터 5,900개가 탑재되어 완전한 32비트 RISC-V 명령 세트를 실행할 수 있다. 하지만 한 번에 작동하는 건 1비트로 제한되기 때문에 연산을 실행하는 데는 32 클록 사이클이 필요하며 클록 주파수도 kHz 단위로 제한되어 있다.

그럼에도 연구팀은 이번에 개발된 이황화몰리브덴 프로세서가 아직 구현되지 않은 실리콘을 대체할 하드웨어 중에서 가장 세련된 것 중 하나라고 주장하고 있다. 하지만 이 프로세서가 기존 실리콘 프로세서를 대체할 것이라고는 생각하지 않으며 단순한 센서용 초저전력 프로세서와 같은 틈새 수요를 충족시킬 가능성이 있을 것으로 예상하고 있다. 관련 내용은 이곳에서 확인할 수 있다.