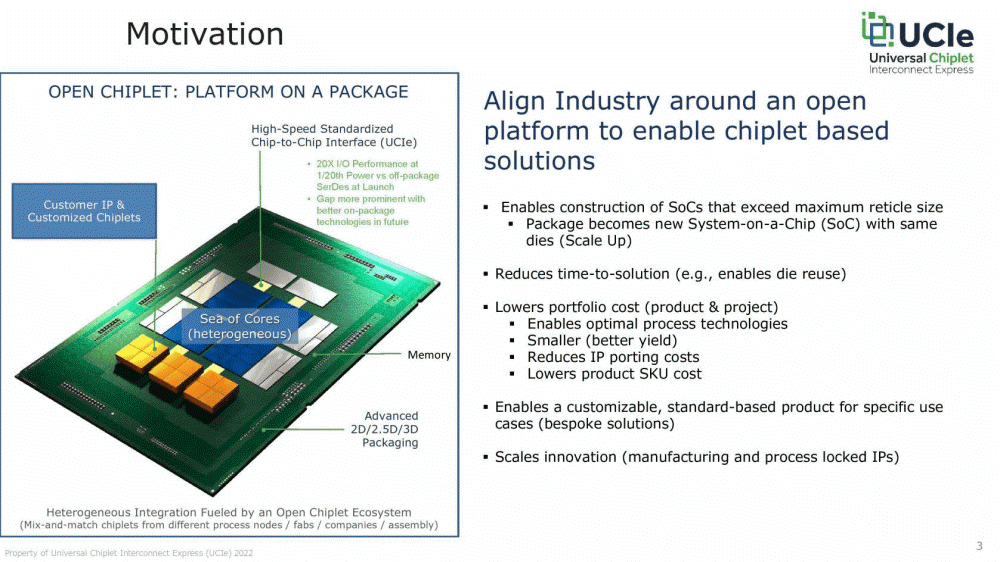

인텔이나 AMD, ARM, 퀄컴, TSMC, 삼성전자 등 반도체 기업과 마이크로소프트나 메타 같은 기술 기업이 모여 별도 프로세스로 생산한 콤포넌트를 조합해 SoC 1개를 구축하는 칩렛(Chiplet)에 대한 새로운 규격을 책정하기 위한 단체인 UCIe(Universal Chiplet Interconnect Express)를 시작했다. 동시에 다수 실리콘 다이를 패키지 하나에 통합하기 위한 개방적이고 상호 운용 가능한 새로운 규격인 UCIe 1.0 사양도 밝혀졌다.

지금까지는 CPU나 GPU, SRAM 등 기능을 모두 실리콘 다이 1장에 담은 SoC(System on Chip)가 만들어졌다. 하지만 1장에 모든 기능을 포함하면 모든 기능을 한 프로세스 노드에서 생산하게 된다. 따라서 각 기능을 적절한 제조고정 노드에서 생산하고 마치 레고 블록처럼 같이 조합해 칩을 설계한다는 개념으로 칩렛이 등장했다.

칩렛은 다이마다 최적 제조공정 노드로 생산해 칩 수율을 높이고 비용 성능을 높일 수 있다는 게 가장 큰 장점이다. 칩렛이 등장한 건 반도체 회로 집적 밀도는 1년 반에서 2년마다 2배가 된다는 무어의 법칙에 한계가 온 가운데 프로세서에 요구되는 성능이 높아져 필연적으로 칩 생산 비용 성능을 더 높일 필요성이 배경이다.

AMD 라이젠 시리즈나 인텔 사파이어 레피드(Sapphire Rapids) 세대 제온 등 이미 칩렛을 설계에 채용한 프로세서는 등장하고 있지만 이런 칩렛에서 사용되고 있는 다이 상호 접속 규격은 다르다. 이번에 제창된 UCIe 규격은 이 다이를 상호 접속하는 방법을 단일 규격으로 정하는 것으로 미래에는 기업이 같은 업종 타사 실리콘 다이를 자사 제품에 넣거나 중소기업이 독자 칩렛 설계를 실시하는 것도 가능하게 된다.

이번에 발표된 UCIe 1.0은 인텔이 개발해 2020년 오픈한 기술(Advanced Interface Bus)을 기반으로 책정되고 있다. 칩렛 다이가 상호 통신하기 위한 전기 신호 규격이나 물리적 레인 수, 범프 피치가 규격화되고 또 상호 통신 프로토콜이 정의되고 있다. 하지만 UCIe 1.0은 칩렛 다이를 상호 연결하는 방법에 대해선 결정했지만 다이와 다이 연결을 어떻게 설계하는지에 대한 패키징 기술과 브리징 기술은 포함되어 있지 않다. 또 UCIe 1.0은 표준 패키지와 고급 패키지라는 2가지 다른 성능 수준을 제공한다. 기존 기판을 상정하고 있는 표준 패키지는 최대 16데이터 레인으로 칩간 공간은 25mm이지만 고급 패키지는 최대 64에이터 레인으로 칩간 공간은 불과 2mm가 된다.

UCIe 기반이 되는 칩렛간 통신 프로토콜은 PCIe와 관련이 있는 CXL(Compute Express Link)가 되고 있다. 하지만 AMD 인피니티 패브릭(Infinity Fabric)과 같이 독자 프로토콜에서도 UCIe 사양에 존거한 채로 사용할 수 있다고 한다.

UCIe에 참가하는 기업은 인텔, AMD, ARM, 퀄컴 같은 팹리스 기업과 TSMC, 삼성전자, ASE그룹 같은 반도체 기업, 마이크로소프트, 구글, 메타 등도 이름을 올리고 있다. UCIe 책정과 보급이 진행되면 인텔 CPU에 AMD GPU를 조합하는 게 가능하게 될지도 모른다. 관련 내용은 이곳에서 확인할 수 있다.