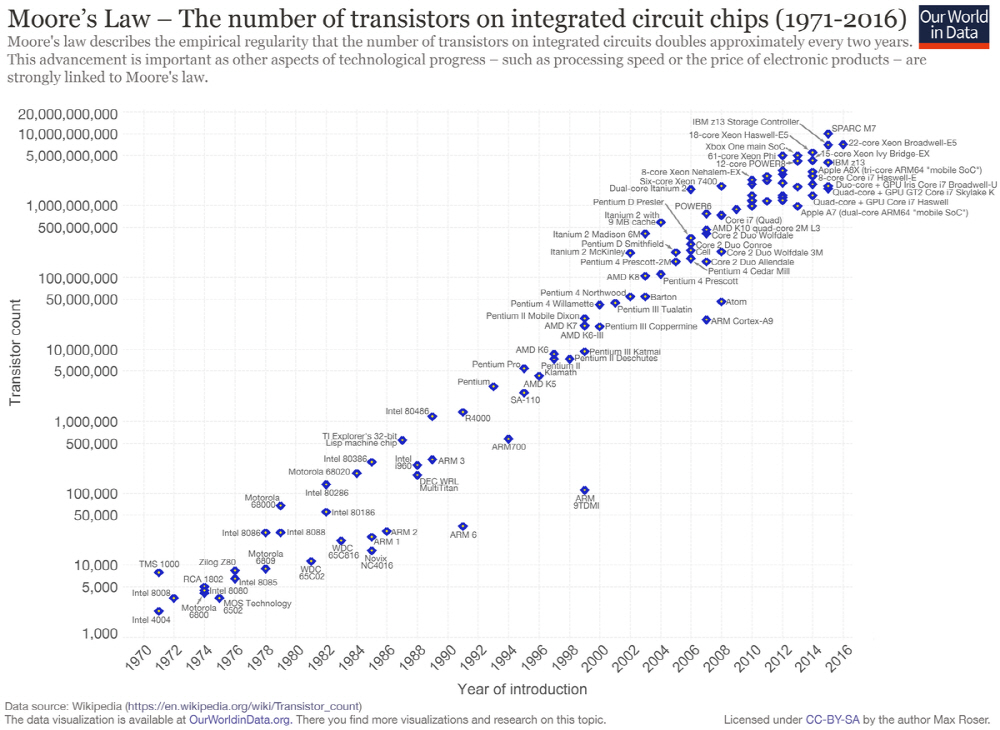

인텔은 지난 2016년 10nm 제조공전 전환이 지연되면서 오랫동안 반도체 산업을 암묵적으로 지배해왔던 무어의 법칙을 유지할 수 없게 되는 것 아니냐는 말이 나오기 시작했다. 무어의 법칙은 반도체 집적회로의 트랜지스터 수는 2년마다 2배가 된다는 것이다. 인텔 창업자 중 한 명인 고든 무어가 페어차일드반도체에서 일하던 1965년 논문을 통해 처음으로 제창한 것이다.

무어의 법칙 자체는 고든 무어의 경험에 근거한 예측이라고 할 수 있지만 이후 반도체 혁신은 거의 무어의 법칙대로 진화를 해왔고 반도체 업계에선 법칙이라고 부를 절대적 지표로 간주되기도 했다. 트랜지스터 수라는 건 다른 말로 바꾸면 성과라고 할 수 있다. 무어의 법칙은 곧 컴퓨터 성능은 18개월마다 2배가 된다고 표현할 수도 있다.

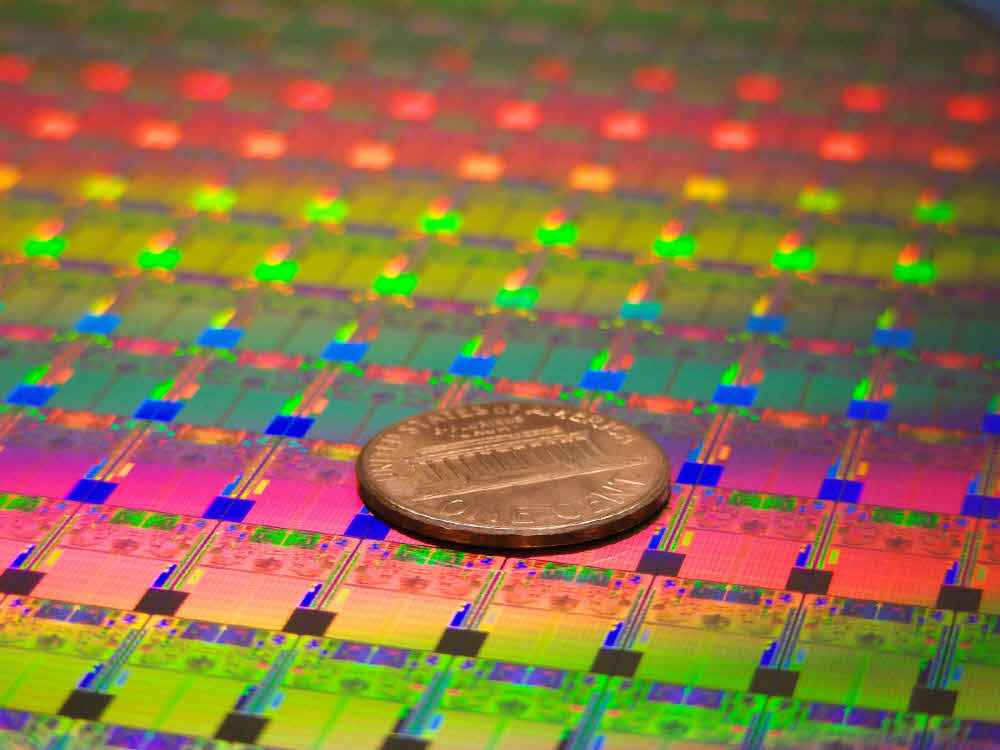

무어의 법칙에 따라 작아진 집적회로는 스마트폰 전성기인 2016년 회로폭이 14nm에 도달하게 된다. 스마트폰은 모바일 기기인 만큼 고성능화 뿐 아니라 사물인터넷 시대를 고려하면 제조공정은 10nm, 7nm 등 더 미세화를 요구하고 있다. 실제로 스마트폰에선 7nm 제조공정이 도입되고 있다.

1960년대부터 50년 이상 반도체 산업에서 통용되어 온 무어의 법칙은 사실 우연이 아니다. 반도체 산업은 기술 진화 지표로 무어의 법칙을 삼아 몇 년 안에 실현할 로드맵을 만들고 개발자 역시 무어의 법칙을 기준으로 해왔다. 다시 말해 무어의 법칙을 지킬 수 있게 기술을 개발하고 법칙이 무너질 것 같으면 돌파구가 될 만한 기술을 만들어내 어떻게든 무어의 법칙을 유지해왔다는 것이다. 업계 모두 무어의 법칙을 유지하겠다는 목표가 있었던 만큼 무어의 법칙은 단순한 결과론이 아니라는 얘기다.

무어의 법칙을 지켜온 반도체 산업이지만 사실 미세화 기술에는 한계가 있는 것도 사실이다. 미세화가 진행되면 소비전력을 줄이기 어려워지고 소비전력에 제약이 생기면 다크 실리콘이라고 불리는 영역이 늘어나는 문제가 덩달아 생긴다. 미세화를 진행하는 어려움이 높아질수록 무어의 법칙을 지키는 건 점점 어려워지는 것이다.

무어의 법칙만 그대로 따르자면 2030년에는 제조공정은 2nm가 되어야 한다. 이 정도라면 원자 10개 분량 수준에 불과하다. 양자적 영향이 지금보다 훨씬 커지는 탓에 전자가 안정적으로 동작하는 걸 기대하기 어렵다. 더 이상 미세화할수록 성능이 높아진다는 단순한 세계를 그릴 수 없는 영역에 도달할 시간이 임박했다는 얘기다.

물론 중요한 건 무어의 법칙이 끝난다고 기술 진화가 끝난다는 건 아니라는 것이다. 예를 들어 보잉 787 같은 최신 기종이 1950년대 등장한 보잉 707을 속도로 이기는 건 아니다. 하지만 성능은 확실히 좋아졌다. 비행기 성능을 단순히 속도 경쟁만으로 말하지 않듯 반도체 성능 역시 집적회로 밀도만으로 얘기해선 안 된다는 얘기다. 결국 무어의 법칙 다음 지표가 필요하다는 얘기다. 단순 연산 능력 이상으로 절전 성능이 중시되거나 여러 칩을 하나로 묶는 패키징 기술 같은 것도 예가 될 수 있다. 반도체 소재로 실리콘을 대체할 탄소나노튜브나 그래핀 같은 탄소 구성 물질을 연구할 수도 있다.

이런 점에서 주목받는 것 중 하나는 RISC-V다. RISC-V는 대학을 중심으로 오픈소스로 개발하는 CPU 명령 세트 아키텍처지만 이젠 마이크로소프트와 IBM, 퀄컴, 마이크론, 삼성, 화웨이 같은 유명 기업이 참여하는 거대한 프로젝트가 됐다.

기존 CPU 개발을 할 때에는 ISA(instruction set architecture. 명령어 세트 아키텍처)는 제한된 기업만 사용할 수 있는 닫힌 존재였다. x86을 예로 들면 인텔과 AMD만, 모바일인 ARM의 ISA를 이용하려면 ARM에게 라이선스 비용을 지불해야 했다. 따라서 칩 개발에 ISA라는 존재는 진입장벽 역할을 해왔다고도 할 수 있다.

이런 닫힌 세상을 개방해줄 존재가 바로 오픈소스로 개발된 RISC-V라고 할 수 있다. RISC-V는 라이선스 수수료가 필요 없기 때문에 사물인터넷 시대가 열리면 맞춤형 기기 개발을 활발하게 불러올 수 있다. 물론 누구나 무료로 쓸 수 있는 RISC-V의 장점은 여기에만 그치지 않는다. 업계 전체를 위해 태어난 생태계라는 점이 그것이다. 이런 점에서 ARM이나 인텔, ARC, 텐실리카 등이 쓰던 과거의 방식에서 탈피해 RISC-V의 역할에 기대를 하는 것이다.

예전에는 코어 그러니까 CPU 업체를 선택해 ISA를 취득하는 방식이었다면 이젠 먼저 ISA, 그러니까 RISC-V를 선택한 다음 제조사를 선택할 수 있다. 다시 말해 제품, 칩마다 서로 다른 제조사를 이용할 수 있다는 얘기다. 오픈소스 코어를 이용하거나 상용 코어를 이용할 수도 있다. 하드웨어를 선택하는 유연성이 생기는 건 물론 제품 설계에도 유연성을 기대할 수 있다.

RISC-V는 산업계와 학계를 이어주는 연계가 가능하다는 장점도 있다. RISC-V가 UC버클리에서 탄생한 이유 중 하나는 산업계에서 탄생한 ISA를 이용한 칩을 개발할 수 없다는 게 한 몫 했다. 학계에선 다른 사람이 만든 지식에 새로운 지식을 얹는 연구 활동이 이뤄지지만 기존 상용 ISA는 특허 등 지적재산권과 복잡하게 얽혀 있다. 다른 사람과 일을 공유하기 어려운 것이다. 따라서 연구를 위해 RISC-V가 탄생했다고 할 수 있다.

RISC-V를 이용하면 산업계에서 발견된 문제는 대학을 비롯한 학계에서 해결책을 찾아 반환해주는 선순환 구조를 기대할 수 있다. 산학 협력을 통해 산업계와 학계의 기술적 일관성이 높아지면 대학에서 연구를 수행했던 연구원이 졸업 이후 산업계로 원활하게 이동할 수 있게 된다. 기업 역시 학술계에서 연구되던 첨단 기술과 경험을 효율적으로 활용할 수 있을 것으로 기대할 수 있다.

RISC-V를 이용하면 산업계에서도 협력이 활발해질 것으로 기대할 수 있다. 과거에서 불가능했던 경쟁 업체와의 협력 혹은 전혀 다른 업계와의 협업을 통해 새로운 가치 창출도 기대해볼 만하다는 것이다.

장기적으로 RISC-V의 성공 여부는 이를 지원할 소프트웨어 생태계에 달려 있다고 할 수 있다. RISC-V 에코 시스템은 아직까지는 ARM 정도는 아니지만 이미 다른 기업이 지닌 지적재산권을 능가한다고 한다. RISC-V를 채택하고 이 플랫폼으로 옮겨온 다수 기업 덕분이라고 할 수 있다. 무어의 법칙이 붕괴되면서 반도체 업계는 새로운 방향성을 찾고 있다. RISC-V 역시 이런 흐름 속에서 존재감을 키우고 있다고 할 수 있다.