무어의 법칙은 반도체 집적 밀도는 18∼24개월마다 2배로 늘어나 칩 성능이 2배가 되어도 더 소형화된다는 것으로 인텔 창업자 중 하나인 고든 무어가 1965년 미래를 예측한 것이다. 이런 무어의 법칙 다음에 올 파도에 대해 인텔 기술 개발 담당 매니저인 앤 켈러허(Ann Kelleher) 부사장이 밝혀 눈길을 끈다.

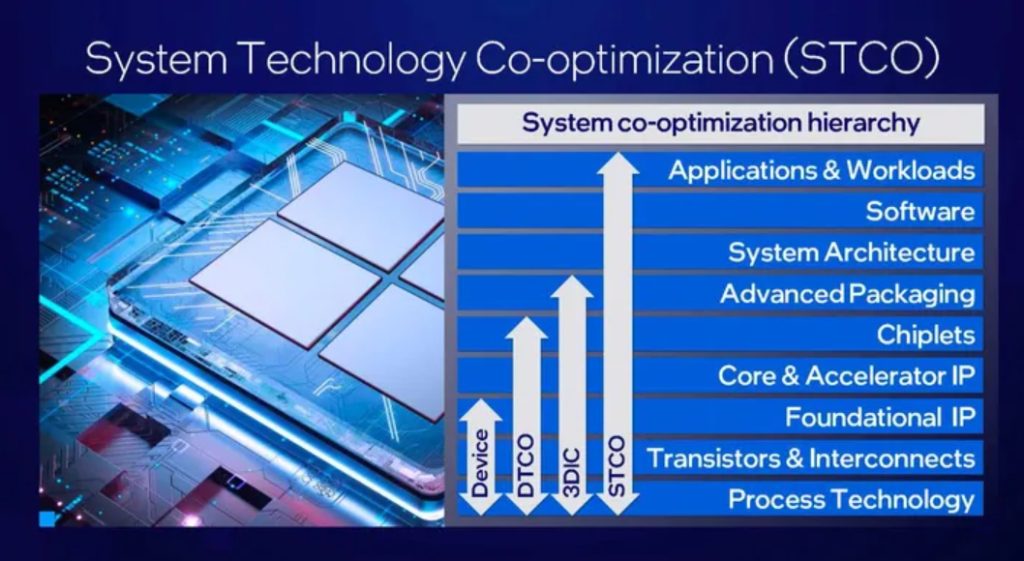

앞으로 10∼20년 뒤를 내다보면 시스템 기술 최적화 STCO(system technology co-optimization)를 들 수 있다. 제품이 지원해야 할 워크로드와 소프트웨어로부터 시스템 아키텍처, 패키지 내에서 요구되는 실리콘, 반도체 제조 공정에 이르기까지 사회나 고객 요구에서 솔루션을 생각하는 아웃사이드인 방식으로 개발해 나간다는 것. 캘러허 부사장은 최종 제품에서 최적의 답을 얻을 수 있도록 모든 요소를 최적화해나갈 것이라고 밝히고 있다.

STCO가 선택권에 들어온 건 이전이라면 칩 하나에 탑재하고 있던 기능을 작은 기능 칩인 칩렛으로 분할해 각각 최적 반도체 제조 공정 기술로 제조한 뒤 고대역폭으로 연결할 수 있게 된 게 가장 큰 요인이다.

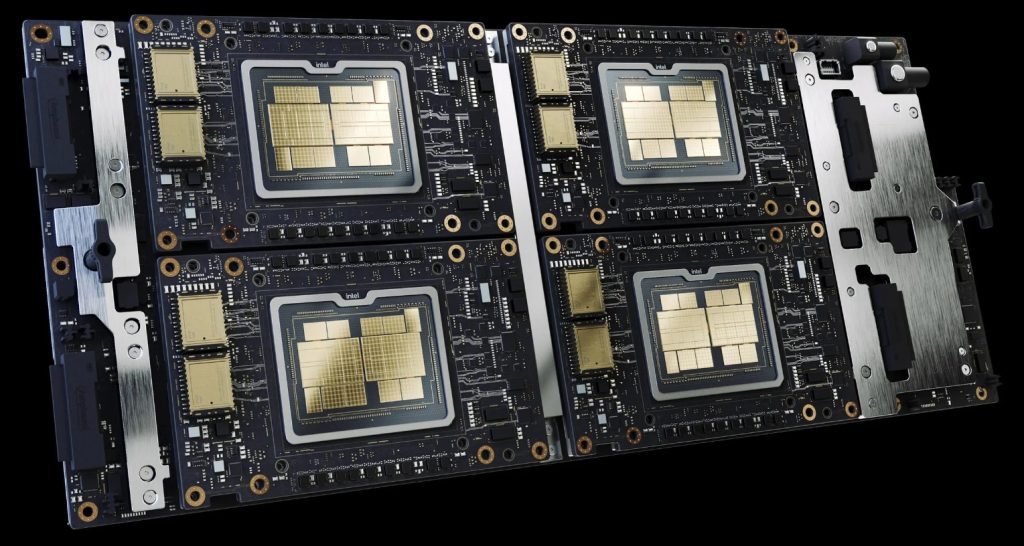

STCO 실용 예로는 슈퍼컴퓨터 오로라(Aurora) 심장부 격인 폰테 베키오(Ponte Vecchio) 프로세서다. 이 프로세서는 47개 액티브 칩렛과 열전도 블랭크 8개로 이뤄져 있으며 고급 2.5D 패키징 기술과 3D 스태킹으로 연결된다. IEDM 2022에서 인텔이 3D 하이브리드 본딩 기술 밀도를 2021년 보고 당시와 비교해 10배 높였다고 발표했다. 연결 밀도가 향상된다는 건 더 많은 칩 기능을 칩렛으로 분해할 수 있다는 걸 말하며 STCO 성과를 더 높일 수 있게 된다. 상호 연결 사이 거리를 보여주는 하이브리드 본드 피치는 3마이크로미터이며 프로세서 코어에서 더 많은 캐시를 분리할 수 있다. 캘러허 부사장에 따르면 본드 피치를 2마이크로미터에서 100나노미터로 줄일 수 있다면 같은 실리콘 상에 있어야 하는 로직 기능도 분리할 수 있다고 한다.

캘러허 부사장은 미래 반도체 공정 기술에서 가장 큰 변화는 인터커넥트 기술이라고 말한다. 인텔은 2024년 파워비아(PowerVia)라는 기술을 도입할 예정이라고 한다. 파워비아는 칩 전력 공급 네트워크를 실리콘 아래로 이동시켜 로직 셀 크기를 줄이고 소비 전력을 줄여준다고 한다.

STCO는 아직 초기 단계에 있으며 전기 회로 설계 EDA 툴이 임하는 건 STCO 전신인 디자인 기술 최적화 DTCO로 로직 셀 레벨과 기능, 블록 레벨 최적화에 중점을 두고 있다고 한다. 켈러허 부사장은 앞으로 STCO를 실현하는 방법과 도구가 주목받을 것이라고 밝히고 있다.

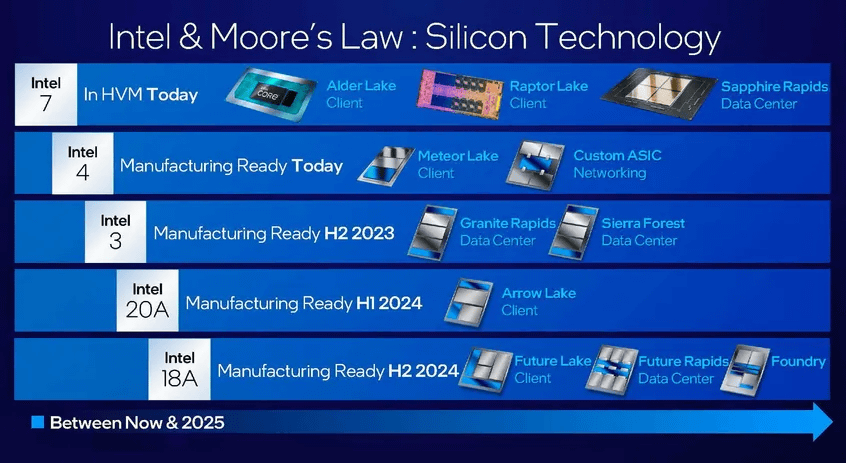

그가 말하는 새로운 인텔 로드맵은 2024년 전반부터 제조 예정인 인텔 20A에서 새로운 트랜지스터 아키텍처인 리본펫(RibbonFET)과 파워비아가 도입된다. 새로운 기술 위험에 대해 그는 파워비아로 이행하는 것으로 리본펫 기술을 실현할 수 있기 때문에 큰 이점이 있다고 밝히고 있다. 기존 아키텍처인 핀펫(FinFET)을 이용한 파워비아 테스트가 순조롭게 개발 작업을 가속화할 수 있게 해줬다고 한다.

더붙여 트랜지스터 미래에 대해 평면형 트랜지스터 설계가 1960년부터 2010년 경까지 살아남고 후속인 핀펫이 건재하기 때문에 켈러하 부사장은 트랜지스터가 100주년을 맞는 2047년에 대해 리본펫 이행 어딘가 시기에 절충하게 될 것으로 본다고 밝혔다. 관련 내용은 이곳에서 확인할 수 있다.