포베로스(Foveros)는 지난 12월 12일(현지시간) 인텔이 아키텍처 데이(Architecture Day) 기간 중 공개한 차세대 CPU 아키텍처에 이용할 칩 기술이다.

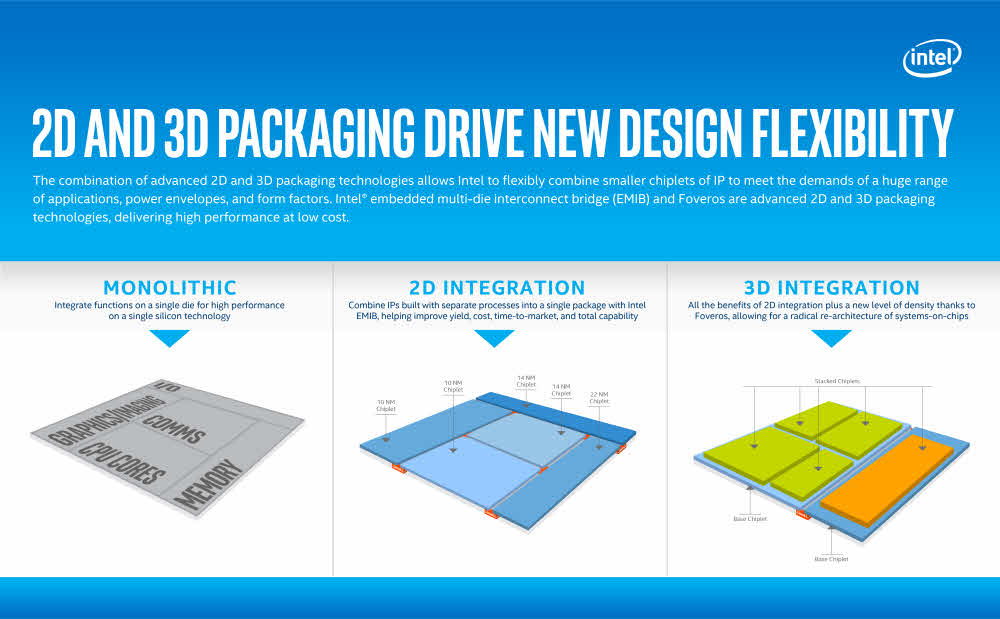

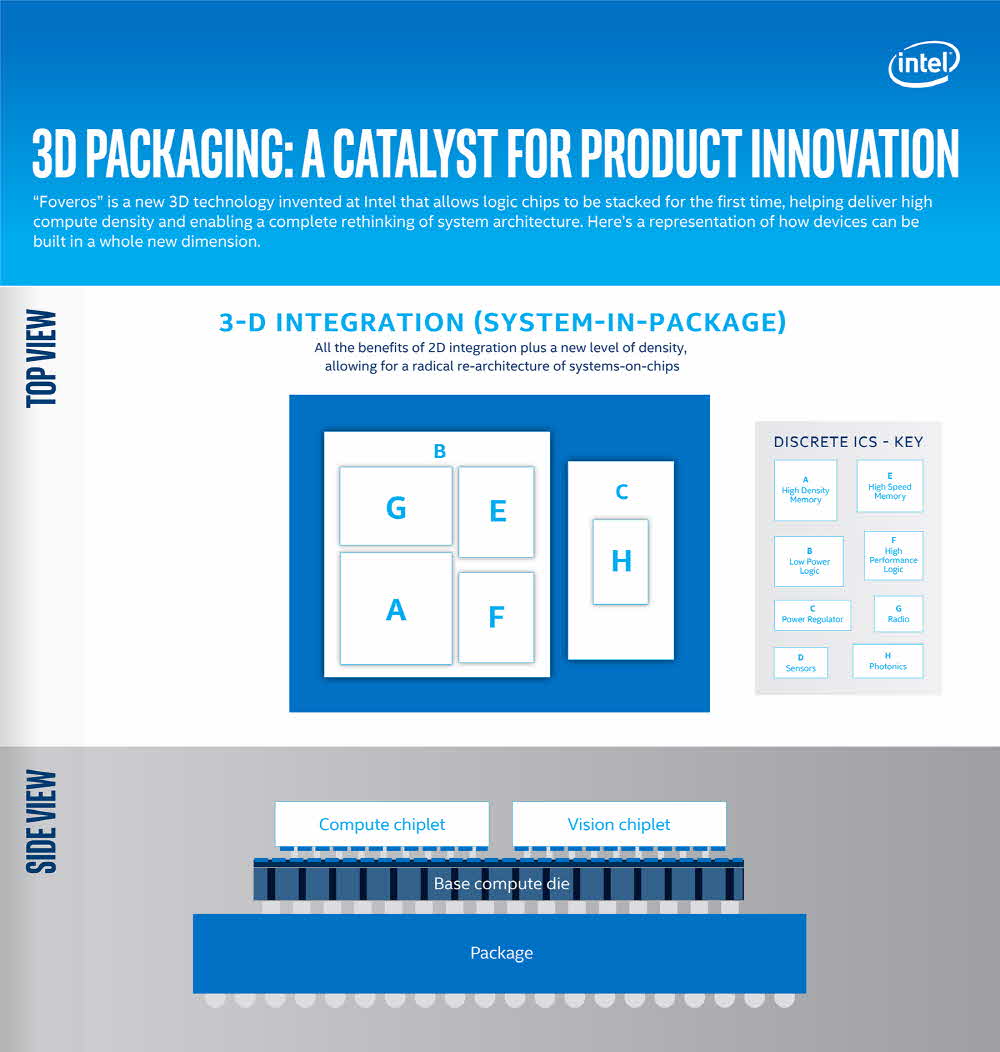

포베로스는 3D 칩 기술이다. 3차원으로 설계 패키징한 집적 회로 적층 기술인 것. 이젠 칩 속에 트랜지스터를 넣을 틈이 점점 사라지고 있어 무어의 법칙도 종말을 맞을 태세다. 이 같은 문제를 해결할 방법 중 하나가 바로 세로 방향으로 트랜지스터를 늘어놓는 것이다.

반도체 패키지에 적층합 칩이라면 AMD의 라데온 R9 퓨리X(Radeon R9 Fury X)를 떠올릴 수 있다. 3D 적층을 이용한 대역폭 메모리 기술 HBM(High Bandwidth Memory)을 이용했다. 하지만 포베로스는 전혀 다른 수준의 기술이라고 할 수 있다. 인텔은 파워 입출력과 전력 공급 등을 맡는 칩에 고성능 로직 칩을 적층해 면적이 작은 적층화가 가능하다고 밝히고 있다.

개발 중인 포베로스 기술을 담은 제품은 22nm 제조공정을 이용한 프로세서에 입출력, 10nm 제조공정 프로세서와 그래픽, 다시 위에 메모리를 적층한 3층 구조가 될 전망이다. 이 기술은 더 작은 공간에 저전력 고효율 칩 설계를 할 수 있게 해준다. 인텔은 포베로스 기술을 이용하는 제품이 어떤 장치에 쓸 수 있을지 방법을 제시하지 않았지만 CPU 공간 절약과 고성능화는 당연히 기대할 수 있다.

포베로스는 실험실 수준 기술이나 프로젝트가 아니라 2019년 하반기 출시될 예정이다. 또 포베로스를 발표한 인텔 수석 아키텍트인 라자 쿠드리(Raja Koduri)는 한때 AMD에서 GPU 개발을 이끌었던 인물이다. R9 퓨리X 역시 그의 개발팀이 만들어낸 것이었다. 관련 내용은 이곳에서 확인할 수 있다.