지난 12월 9일부터 13일까지 미국 샌프란시스코에서 열린 IEEE 행사인 IEDM에서 삼성전자, 인텔, TSMC가 CMOS 메모리를 소형화하기 위한 기술인 CFET 데모를 각각 공개했다.

CFET을 가장 빨리 입증한 건 인텔로 2020년 IEDM에서 초기 버전을 발표한 바 있다. 이번에 인텔은 CFET에서 가장 단순한 회로인 CMOS 인버터에 대해 몇 가지 개선점을 보고했다. 인버터는 단일 레이어에서 이뤄지며 일반 CMOS 인버터에서 최대 50% 크기를 줄일 수 있다는 설명이다.

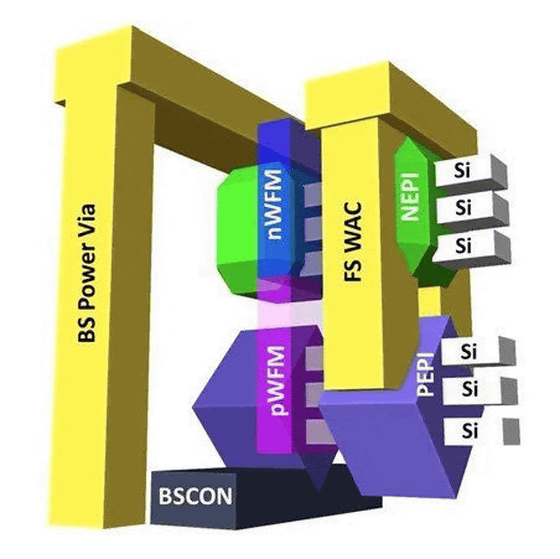

인텔은 2023년 6월 인텔 파워비아(Intel PowerVia)라는 기술을 제품 버전 테스트 칩에 구현한다고 발표했다. 인텔 파워비아는 트랜지스터층 뒷면에서 전원 공급을 할 수 있게 해 회로를 대폭 간소화할 수 있다. 그 결과 CMOS 인버터는 CPP라고 불리는 트랜지스터 게이트 피치를 60nm까지 줄일 수 있었다고 한다. 인텔은 파워비아 기술이 이미 양산 준비를 완료, 탑재 제품을 2024년 등장시킬 예정이라고 한다.

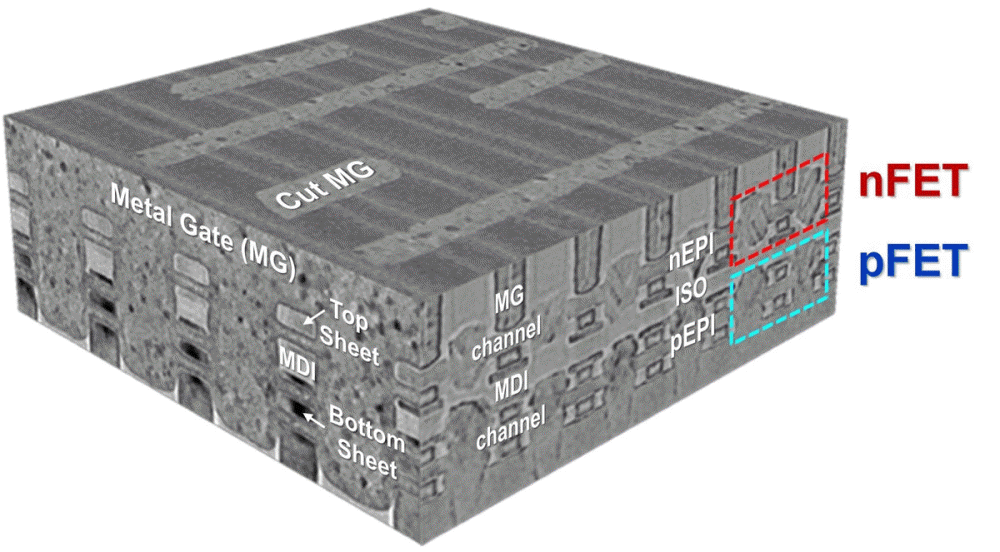

인텔은 또 기기당 나노시트 트랜지스터 수를 2층에서 3층으로 늘리고 기기간 피치를 50nm에서 30nm로 줄이고 기기 접속 부분에 개선된 형상을 사용해 CFET 전기 특성이 개선됐다고 보고했다.

그 뿐 아니라 인텔은 2021년 제조공정 규칙을 검토했을 때 핀펫(FinFET) 이후에는 게이트 올어라운드 나노시트 구조를 채택한 리본펫(RibbonFET)을 앞으로 도입할 것이라고 밝혔다. 이번 행사에서 인텔은 리본펫에 대해서도 입증했으며 트랜지스터 스위칭 속도가 빨라지고 주파수와 성능이 향상된다고 보고했다.

삼성전자는 CPP를 48nm 또는 45nm까지 줄일 수 있었다고 발표했다. 삼성전자 프로포타입 CFET 중 CPP는 45mm인 부분은 성능 저하가 보였지만 삼성전자는 제조공정 최적화로 해결할 수 있는 문제라고 밝혔다. 삼성전자는 화학약품에 의한 에칭을 개선해 nFET와 pFET 절연을 실현하고 동시에 기기 수율을 80% 향상시킬 수 있었다고 한다.

삼성전자는 또 인텔과 마찬가지로 트랜지스터층 뒷면에서 전원 공급을 할 수 있게 하는 기술을 채택했다. 하지만 인텔이 나노시트를 3층으로 한 반면 삼성전자는 나노시트 트랜지스터 1층으로 실현했다. 삼성전자는 나노시트 트랜지스터 수를 늘리면 CFET 성능이 더 향상된다고 밝혔다.

TSMC도 나노시트 트랜지스터 에칭을 고안해 나노시트에 효율적으로 절연층을 구축해 CPP 48nm 수준에 도달하는데 성공했다고 보고했다. 참고로 제조사마다 CFET을 실용화하기 위한 기술을 개발하고 있지만 실제로 CFET이 상업적으로 전개되는 건 빨라도 2030년 이후로 예상된다. 관련 내용은 이곳에서 확인할 수 있다.